Total

Search

1. 제어장치의 개요

1.1. 제어장치의 정의 및 역할

•

제어 장치의 정의

◦

컴퓨터 시스템의 모든 장치들을 유기적으로 제어하는 장치

•

제어 장치의 역할

◦

기억장치에 저장된 프로그램으로부터 명령어를 순차적으로 하나씩 읽어내어 연산코드 부분을 해독한 후,그결과에 따라 컴퓨터 시스템의 각 요소를 동작시키는 제어신호를 발생시켜 명령어를 수행한다.

▪

하나의 명령어는 한 클럭 동안에 수행되는 마이크로 연산의 집합으로 구성

▪

명령어의 실행은 이러한 마이크로 연산의 연속적인 반복으로 이루어짐

◦

요구되는 마이크로연산을 연속적으로 수행하게 하는 신호를 보내어 명령어를 수행하게 함

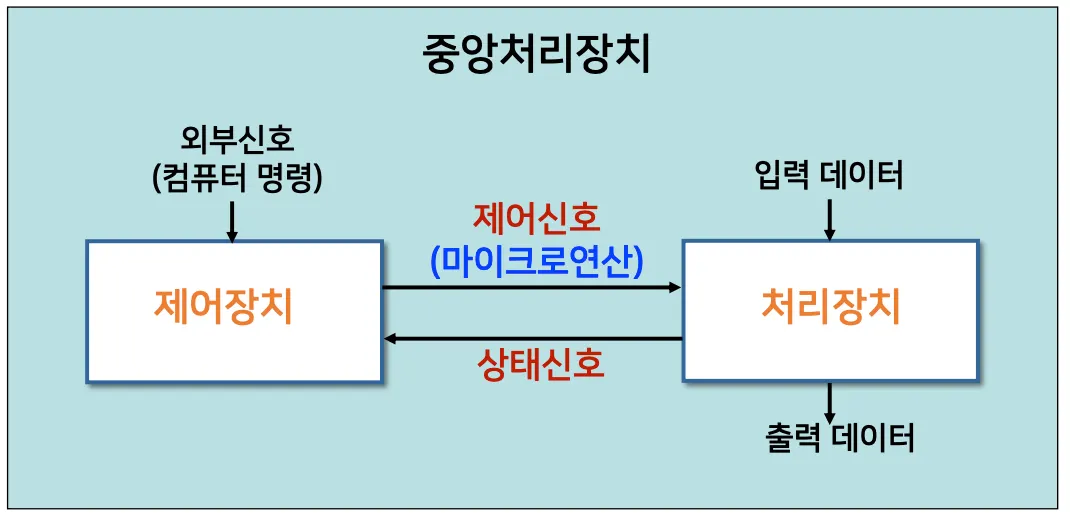

1.2. 제어장치와 처리장치의 관계

•

제어장치와 처리장치의 관계

2. 제어장치의 구성

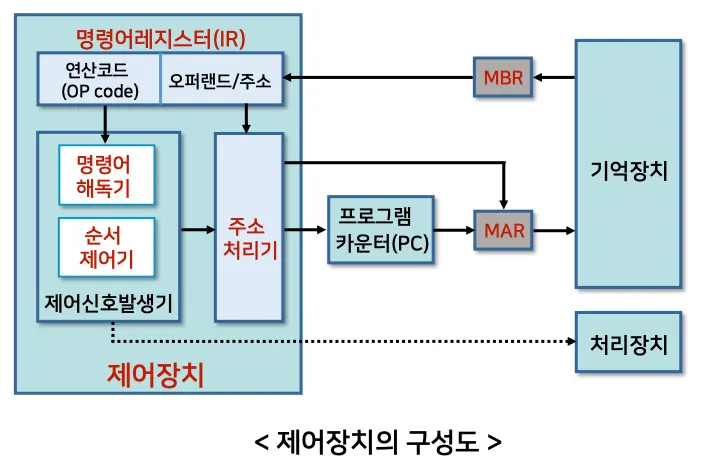

2.1. 제어장치의 구성요소

•

명령어 레지스터 (IR)

◦

연산코드(OP Code)

◦

오퍼랜드(Operand / 주소)

•

제어신호 발생기

◦

명렁어 해독기

◦

순서 제어기

•

주소 처리기

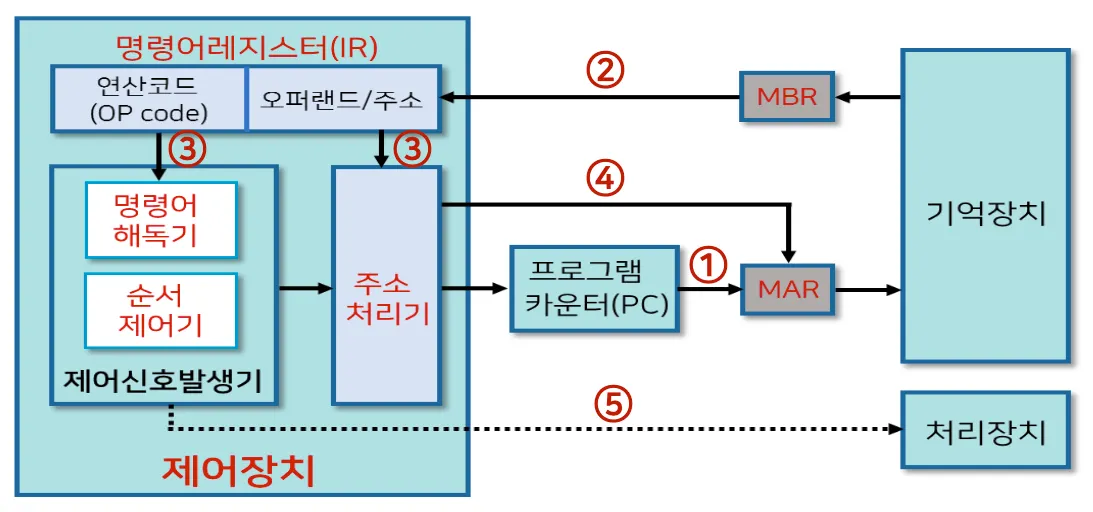

2.2. 제어장치의 동작 (명령어 수행과정)

1.

프로그램카운터(PC)에 저장된 주소로 기억장치에 접근한다.

2.

기억장치에서 명령어를 읽어와 명령어 레지스터(IR)에 저장하고, 프로그램 카운터를 1 증가시킨다.

3.

읽어온 명령어에서 연산코드(오피코드)는 명령어 해독기로, 오퍼랜드는 주소처리기로 보낸다.

4.

주소처리기는 명령어 수행에 필요한 오퍼랜드의 주소 또는 다음 명령어의 주소를 계산한다.

5.

제어신호 발생기에서 연산코드를 해독하여 명령어 수행을 위한 제어신호를 발생한다.

3. 제어장치의 구현

3.1. 제어장치의 유형

•

마이크로 프로그램에 의한 제어장치

◦

제어단어와 같은 제어정보를 특별한 기억장치에 기억시킨 구조

◦

프로그램에 의한 제어방식

▪

장점: 제어신호를 수정하고자 할 때 융통성이 뛰어남

▪

단점: 기억장치에서 명령을 인출하는 별도의 시간 때문에 속도가 느림

◦

고밀도 집적회로(VLSI)가 가능하여 대부분의 컴퓨터에서 사용

•

하드웨어에 의한 제어장치

◦

순서회로와 같은 게이트와 플립플롭(flip-flop)으로 이루어짐

▪

장점: 순서회로로 구성되기때문에 고속동작이 가능

▪

단점: 회로의 동작 방법이 바뀌면 다시 설계해야함

◦

특수한 컴퓨터에서 사용

3.2. 마이크로 명령어 형식

•

마이크로명령어

◦

마이크로프로그램에 의한 제어방식에서 제어기억장치에 있는 제어단어의 내역

•

마이크로명령어의 구성내역

◦

8개의 필드로 구성

▪

16비트 - 처리장치 구동하기 위한 제어 단어

▪

10비트 - 제어장치 안에서 마이크로 연산 수행하기 위한 필요로 하는 비트

▪

A 필드: 처리장치의 레지스터 중 하나의 출발 레지스터 선택

▪

B 필드: 처리장치의 레지스터 중 다른 하나의 출발 레지스터 선택

▪

D 필드: 처리장치의 레지스터 중 도착 레지스터 선택

▪

F 필드: 처리장치의 ALU 연산 선택

▪

H 필드: 처리장치의 시프트 연산 선택

▪

MUX 1 필드: 0과 1로서 내부와 외부 주소를 선택

▪

MUX 2 필드: 상태비트의 값에 따라 CAR을 구동

▪

ADRS 필드: ROM(제어기억장치)의 2진 번지에 해당하는 10진 주소

•

64 x 26

•

64개 → 2^6 로 6비트로 주소값 저장

•

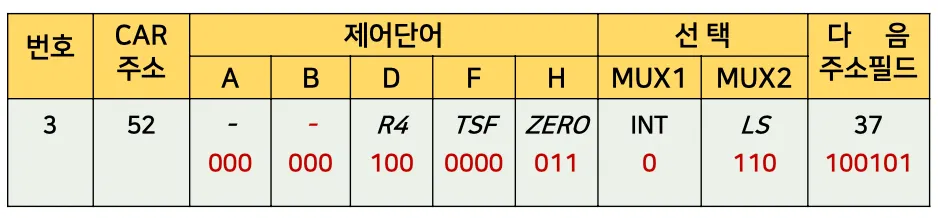

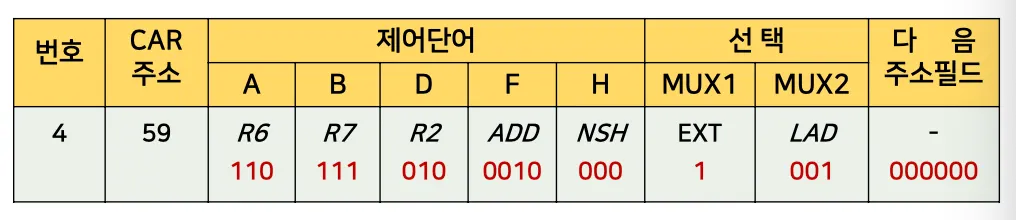

마이크로명령어 형식의 예

◦

각필드의 내역

◦

MUX 2의 선택기능

•

마이크로명령어의 예 (마이크로프로그램이 아님)

◦

주소 36에 저장되어있는 마이크로명령어

▪

R1 ← R1^R2, CAR ← CAR+1

◦

주소 40에 저장되어있는 마이크로명령어

▪

R3 ← R3-1, CAR ← 43

◦

주소 52에 저장되어있는 마이크로명령어

▪

R4←0, if (S=1) then(CAR←37) else (CAR←CAR+1)

◦

주소 59에 저장되어있는 마이크로명령어

▪

R2←R6+R7, CAR←외부주소

3.3. 마이크로프로그램의 작성

•

마이크로프로그램이란?

◦

제어기억장치에 저장된 일련의 마이크로명령어들의 집합

→ 마이크로프로그램 루틴

◦

이러한 마이크로프로그램을 이용하여 제어장치를 구현

→ 마이크로프로그램에 의한 제어장치

•

작성 예

◦

레지스터 전송문

▪

마이크로프로그램 루틴은 20번지에서 시작하여 외부번지로 분기한다고 가정

◦

기호 마이크로프로그램

◦

2진 마이크로프로그램

•

마이크로프로그램의 개념

◦

제어장치 설계를 위한 시스템적인 접근과정

◦

마이크로명령어 형식을 설정하면 마이크로프로그램의 작성과정은 컴퓨터 프로그램 작성과정과 유사

◦

이러한 이유로 펌웨어라고 함

4. 마이크로 프로그램에 의한 제어장치

4.1. 제어단어와 처리장치

•

제어방식

◦

제어변수 값들을 여러 개의 단어로 결합하여 표현하고, 그것을 연속적으로 읽어서 제어 논리 회로에 공급하여 동작시키는 방식

•

제어장치의 역할

◦

일련의 마이크로 연산을 순차적으로 수행하도록 제어

◦

이러한 제어를 위해 제어변수로서 제어단어를 사용

•

제어단어

◦

[A][B][D][F][H] 와 같이 선택신호들의 명령어로 구성되어있음

◦

0과 1의 스트링으로 표현

◦

하나의 명령어를 의미

◦

각 제어단어에는 마이크로 명령어 (microinstruction)가 포함

▪

마이크로 명령어는 하나 혹은 다수의 마이크로 연산을 나타낸다.

◦

제어단어를 이용하여 처리장치의 여러 구성요소들이 특정 시점에서 연산을 시작하도록 프로그램이 가능

•

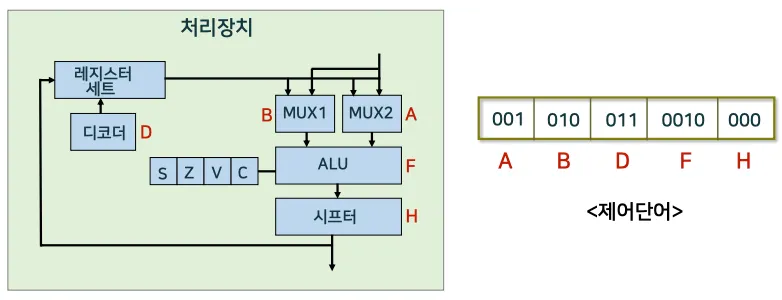

제어단어와 처리장치

◦

제어단어를 구성하는 비트수

▪

16비트 (3+3+3+4+3)

◦

마이크로 프로그램

▪

제어기억장치에 저장된 제어단어들의 집합

▪

제어기억장치에 일련의 제어단어들을 보관

•

제어단어들 = 마이크로 명령어

▪

이 전체를 마이크로 명령어로 구성된 프로그램 → 마이크로 프로그램

•

제어 신호

◦

제어단어를 기반으로 전달하는 신호. 주소값도 포함…

4.2. 제어장치의 구성요소

•

제어기억장치

◦

모든 제어정보를 항상 영구적으로 저장하고 있는 기억장치(ROM)

◦

마이크로 명령어들이 저장되어 있음

◦

저장된 마이크로 명령어는 하나 또는 다수의 마이크로 연산을 나타내는 제어단어를 포함하고 있음

◦

마이크로 명령어가 모두 수행되고 나면, 다음에 수행될 마이크로 명령어의 주소를 결정해야 함

◦

다음 마이크로 명령어의 주소를 결정하기 위해서는 주소 정보가 현재의 마이크로 명령어 내에 한 비트 혹은 여러 비트로 있어야 함

•

다음 주소 생성기 (순서기)

◦

다음에 수행될 마이크로 명령어의 주소를 만들어 냄

◦

이 주소는 다음 클럭 펄스가 입력될 때 CAR로 이동되어 ROM으로부터 다음 마이크로 명령어를 읽어내는데 사용됨

◦

따라서 마이크로 명령어 내에는 처리장치의 마이크로 연산을 실행시키는 제어 비트와 실행될 마이크로 명령어의 순서를 정하는 비트가 포함되게 됨

◦

다음 마이크로 명령어의 주소는 순서기의 입력에 따라 다양한 방법으로 결정 될 수 있음

1.

CAR의 1 증가

2.

제어기억장치의 주소를 제어주소레지스터(CAR)로 적재

3.

외부로부터 온 주소를 제어주소레지스터(CAR)에 적재

4.

제어동작을 시작하는 초기주소 적재

•

제어 주소레지스터 (CAR: Control Address Register)

◦

제어기억장치에 있는 마이크로 명령어의 주소를 나타냄

◦

다음에 읽을 마이크로명령어의 주소를 제어하는 레지스터

•

제어 데이터레지스터 (CDR: Control Data Register)

◦

제어기억장치에서 읽어온 마이크로 명령어를 저장

◦

다음 주소가 계산되어 다음 마이크로 명령어가 제어기억장치로부터 읽혀질 때까지 현재의 마이크로 명령어를 저장

◦

시스템의 간소화를 위해 일반적으로 생략

•

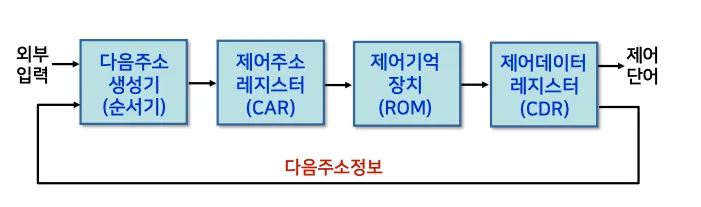

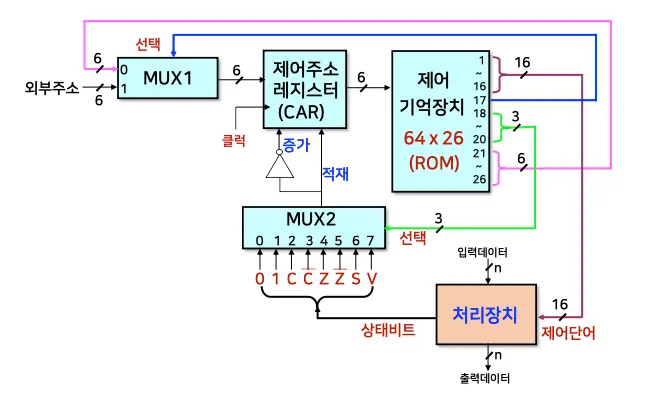

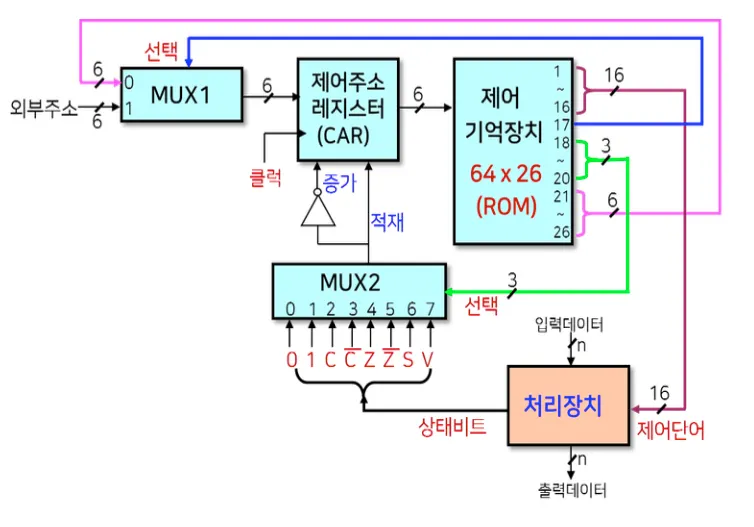

구성도 (1)

•

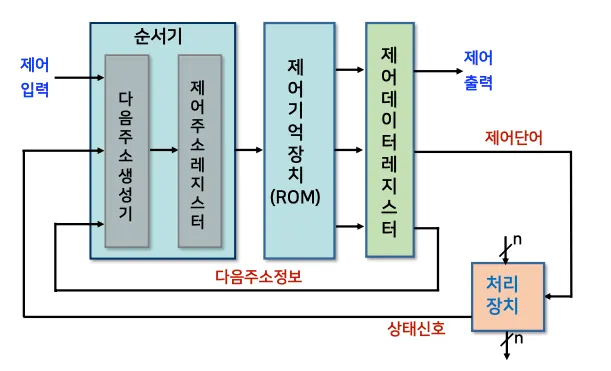

구성도 (2)

•

구성도 (3)

4.3. 제어장치의 동작

•

제어기억장치에 저장된 마이크로명령어(제어단어 포함)에 의해 동작

◦

제어단어만 있는게 아님 → 연산밖에 못함

◦

수많은 마이크로연산을 하려면 마이크로명령어들이 프로그램으로 준비되어야함

•

마이크로명령어 내역 예)

◦

모두 26비트로 구성됨 (제어신호)

▪

처리장치 제어를 위한 16비트 (제어단어)

▪

다음주소 선택을 위한 10비트

•

제어신호 26비트의 구체적인 내역

◦

16비트(1~16)

▪

처리장치 제어를 위한 제어단어

◦

1비트(17)

▪

MUX1에서 외부에서 입력한 주소와 내부 마이크로명령어의 주소 중 하나를 선택

▪

외부 주소냐 내부 주소냐 결정할 때 씀

◦

3비트(18~20)

▪

MUX2의 8개 입력 중 하나를 선택

▪

C,Z,S,V - 상태 레지스터 값이 처리장치에서 옮겨져서 MUX2에 사용됨

◦

6비트(21~26)

▪

ROM의 64단어를 선택하기 위한 주소 비트

▪

cf) ROM의 기억 공간: 제어신호의 갯수가 64개 → 64 x 26

•

제어장치의 동작

1.

처리장치에서 만들어진 상태값(상태비트) 에 의해서 MUX2를 구동시킴

a.

현재 들어있는 주소값을 1 증가시킬건지 (즉, 다음주소), 아니면 현재 들어있는 주소값을 그대로 쓸건지 (적재)를 결정

2.

순서기에 의해 정해진 다음 주소값이 제어주소 레지스터(CAR)로 옮겨짐

3.

CAR에 새로운 주소가 들어오면, 이 주소에 있는 26비트의 마이크로 명령어를 제어기억장치로부터 인출

4.

마이크로 명령어의 제어단어는 CAR의 다음 동작을 결정

5.

처리장치에서 해당하는 상태비트를 새로운 값으로 갱신하며, 다음 주소를 CAR로 전송

6.

CAR의 새로운 주소는 제어 기억장치의 다음 마이크로 명령어를 지정

7.

이러한 과정을 각 클럭의 천이 때마다 반복

•

구성요소별 제어장치의 동작

◦

MUX 1

▪

외부주소(외부기억장치 RAM)나 내부주소(제어기억장치의 주소값) 중의 하나를 선택

▪

선택신호=0

•

현재의 마이크로 명령어의 주소부분을 CAR로 적재

▪

선택신호=1

•

외부주소를 CAR로 적재

◦

MUX 2

▪

상태비트의 값에 따라 CAR의 동작을 결정

▪

선택신호 3비트

•

MUX2의 입력중 하나를 선택하여 CAR에서 수행될 동작을 결정

5. 하드웨어에 의한 제어장치

5.1. 하드웨어에 의한 제어장치

•

정의

◦

주어진 시간에 처리장치에서 수행할 마이크로연산을 결정해주는 제어상태를 갖는 순서회로

•

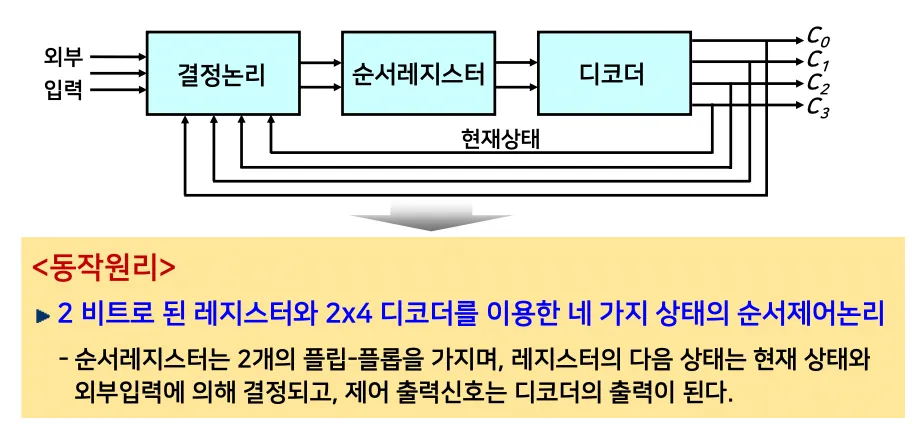

블럭도

5.2. 제어장치의 설계

•

입력신호들에 따라 출력신호들을 발생하도록 내부논리 설계

•

각 제어신호에 대한 부울 표현식이 입력함수로 구현

•

결국 제어장치의 설계는 순서회로의 설계

•

일반적으로 제어순서의 상태도를 이용하여 설계

5.3. 제어장치의 구현 방법

1.

상태 플립-플롭을 이용한 제어방식

•

구성도

2.

순차 레지스터와 디코더를 이용한 제어방식

•

구성요소

◦

레지스터: 제어상태의 순서를 정하는데 사용

◦

디코더: 각 상태마다 하나의 출력만을 나오도록 사용

◦

n-비트 순서 레지스터: n개의 플립-플롭과 게이트로 구성

•

구성도

5.4. 하드웨어에 의한 제어 장/단점

•

장점

◦

순서회로를 사용함으로써 부품의 수는 최소화

◦

동작속도 극대화

•

단점

◦

시스템이 복잡해지면 설계 변경이 어려움

◦

한번 구성되면 바꾸기 어려움

→ RISC 방식에 사용